# A Generic Test Tool for Power Distribution Networks

Istvan Novak, Oracle Peter J. Pupalaikis, Teledyne LeCroy

#### **SPEAKERS**

#### **Istvan Novak**

Senior Principle Hardware Engineer, Oracle istvan.novak@oracle.com | www.oracle.com

#### Peter J. Pupalaikis

Vice President, Technology Development, Teledyne LeCroy peterp@lecroy.com | www.teledyne.com

- Introduction

- Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

#### Agenda

#### Introduction

- Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

#### Introduction

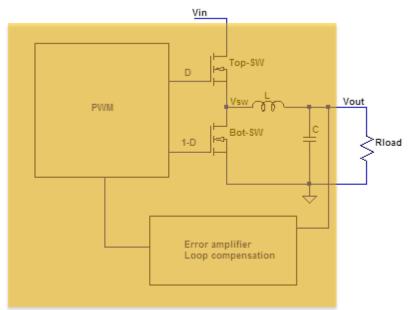

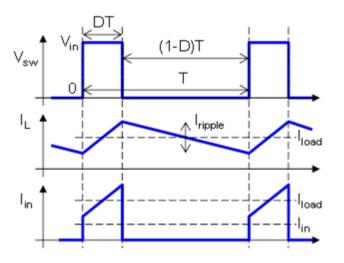

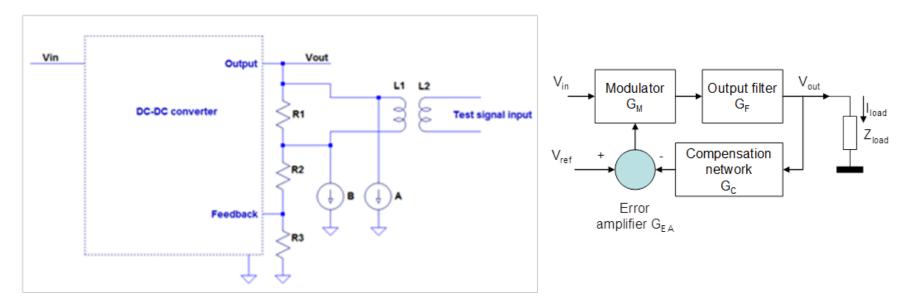

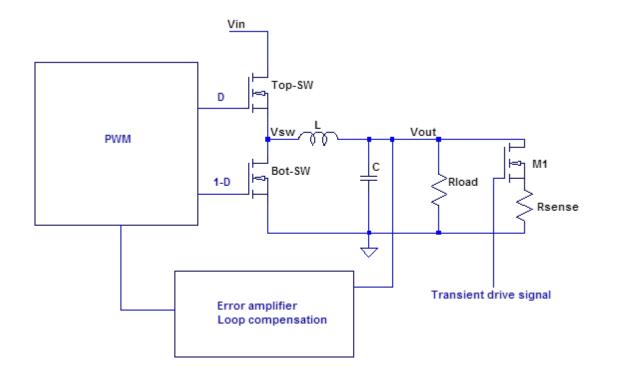

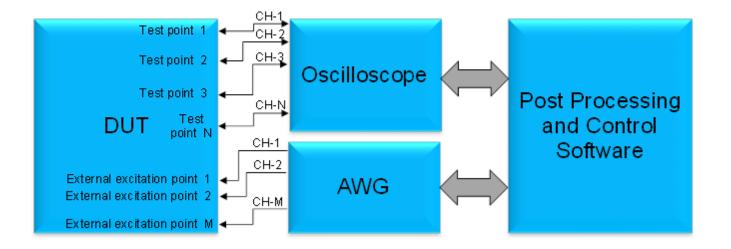

# Non-isolated single-phase buck converter

#### Typical waveforms

# Agenda

#### Introduction

#### Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

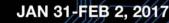

# Input and Output Current, Current Sharing

Options:

- Inductor current with R-C

- Voltage drop across low-side FET

- Voltage drop across high-side FET

- Voltage drop across shunt element

- Current sensor, shunt

# **Voltage Loop Gain**

$G_{loop} = G_M \ G_F \ G_C \ G_{EA}$

#### **Transient Response to Load Current**

#### **Output and Input Impedance**

UBM

#### Input-to-Output and Output-to-Input Transfer

# Agenda

#### Introduction

- Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

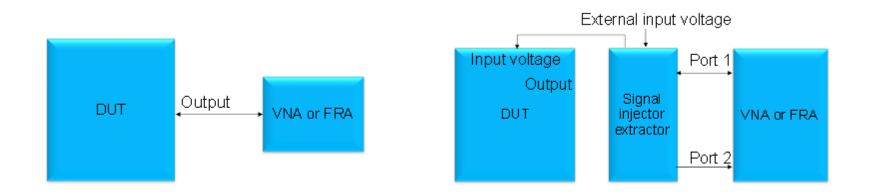

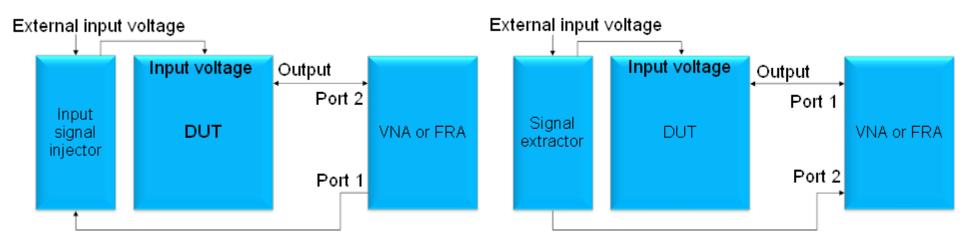

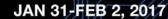

#### **Universal PDN Test Tool, Concept**

# Agenda

- Introduction

- Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

### Implementation

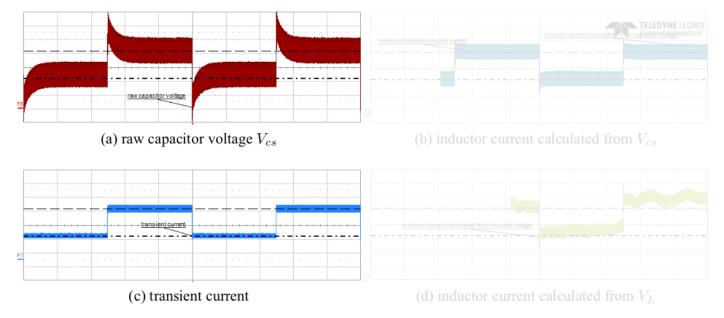

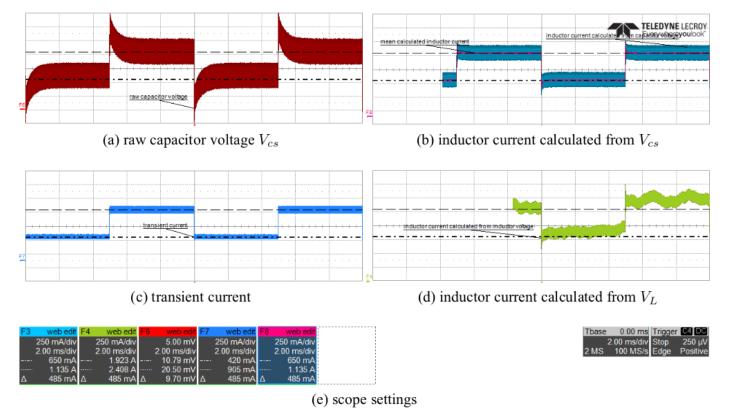

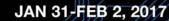

#### Voltage Monitoring Points:

- $\circ$  Vsw the switch node voltage

- Vcs the differential voltage across Cs

- Vout the output voltage

- Goal:

- To correlate the inductor current inferred from VL (Vsw-Vout) and the inductor current inferred from Vcs.

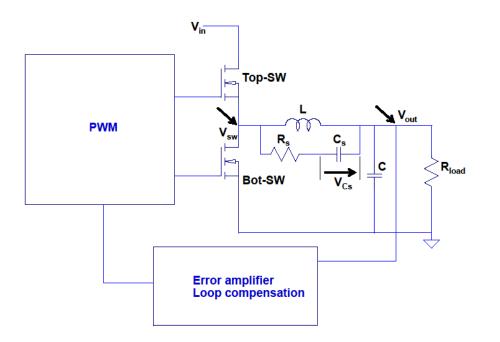

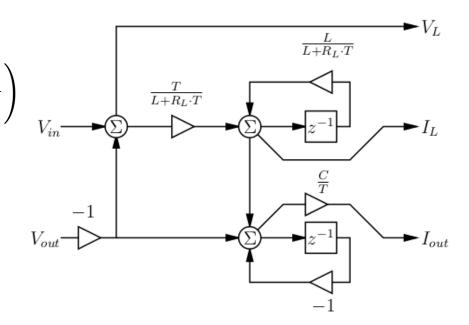

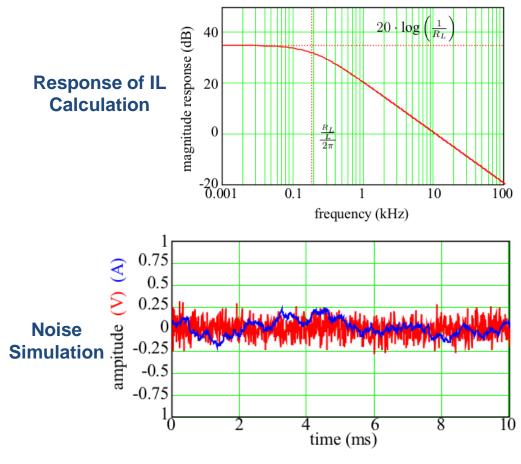

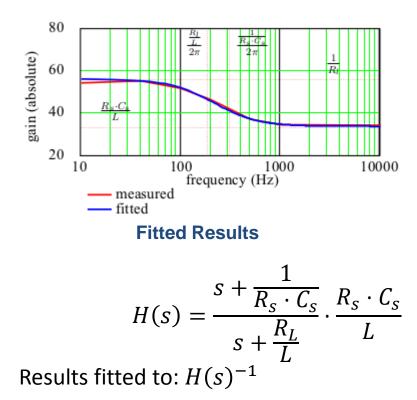

### **Calculation of IL**

$$\tau = \frac{L}{R_L} = \frac{15\mu}{26.4m} = 568.2\mu s$$

$5 \cdot \tau = 2.841 ms = 284.1 kS@100 MS/s$

UBM

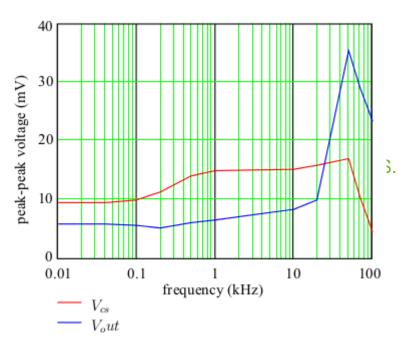

### **Noise Considerations**

Extreme gain at DC

•

$$Gain = 20 \cdot \log\left(\frac{1}{R_L}\right)$$

Noise Density depends heavily on VDIV:

•  $N_{dBm} = 20 \cdot \log\left(\frac{VDIV \cdot 4}{\sqrt{2}}\right) + 13.010 - SNR - 10 \cdot \log(F)$

Effect of noise is not necessarily

intuitive, but can be simulated.

The expectation for this application is a low frequency wander of +/- 250 mA.

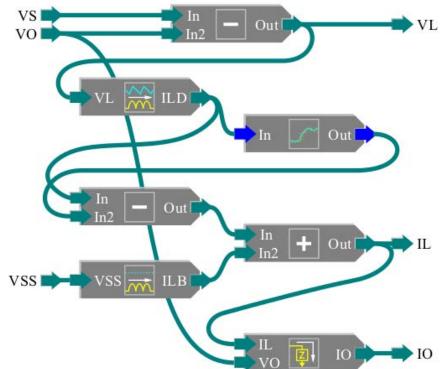

### **Full Inductor Current Processing**

#### Makes use of the LeCroy Processing Web

- Many special purpose components wired together to produce various output waveforms.

- Dynamic Current:

- Calculated by processing VL (the difference between Vsw and Vout)

- Filtered to remove low frequency wander (i.e. High pass filter with single pole cutoff around 10 kHz.).

- Static Current:

- o Sample switch node waveform at flat spot during off time.

- The static and dynamic currents are summed to form IL

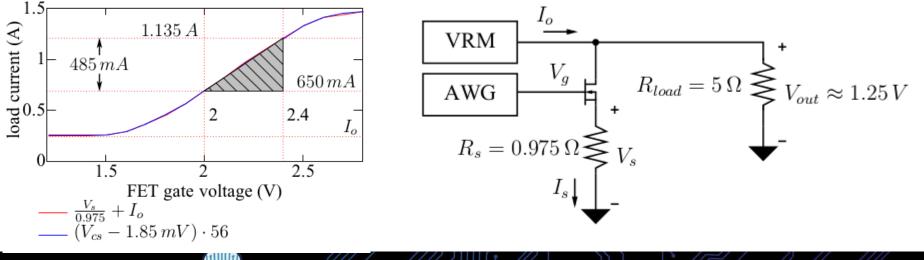

#### **Transient Load Circuitry**

Constant static 5 Ohm load.  $I_{out} \approx \frac{1.25}{5} = 250 mA$

Dynamic Load controlled by FET of up to a parallel 0.975 Ohms.

Vs is monitored with scope

JAN 31-FEB 2, 2017

### **An Unlikely Capacitor Voltage Measurement**

| F | 3 web edit  | F4 | web edit    | F6 | web edit    | F7 | web edit    | F8 | web edit    |  |

|---|-------------|----|-------------|----|-------------|----|-------------|----|-------------|--|

|   | 250 mA/div  |    | 250 mA/div  |    | 5.00 mV     |    | 250 mA/div  |    | 250 mA/div  |  |

|   | 2.00 ms/div |    | 2.00 ms/div |    | 2.00 ms/div |    | 2.00 ms/div |    | 2.00 ms/div |  |

|   | 650 mA      |    | 1.923 A     |    | 10.79 mV    |    | 420 mA      |    | 650 mA      |  |

|   | 1.135 A     |    | 2.408 A     |    | 20.50 mV    |    | 905 mA      |    | 1.135 A     |  |

| Δ | 485 mA      | Δ  | 485 mA      | Δ  | 9.70 mV     | Δ  | 485 mA      | Δ  | 485 mA      |  |

(e) scope settings

0.00 ms Trigger 2.00 ms/div Stop

#### **AC Calibration of IL**

**AC** Calibration

#### **Correct Calculation of IL**

#### **Correct Calculation of IL**

UBM

#### **Disclaimer**

- In the development of this paper we worked rapidly in a manner to explore various measurement possibilities and sometimes handled metrology and full measurement accuracy somewhat loosely.

- This most certainly results in measurement inaccuracies that will be addressed in the future and should not reflect badly on the DUT.

- The results shown are our best efforts at reasonable calibration but are mostly indicative of potential instrument capabilities that can be provided in the future.

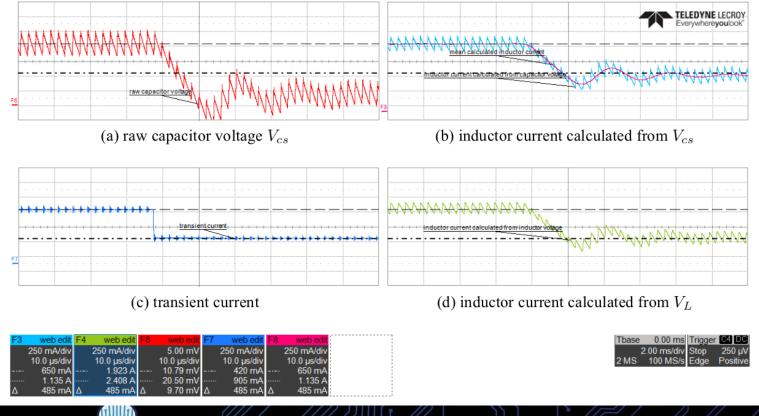

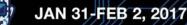

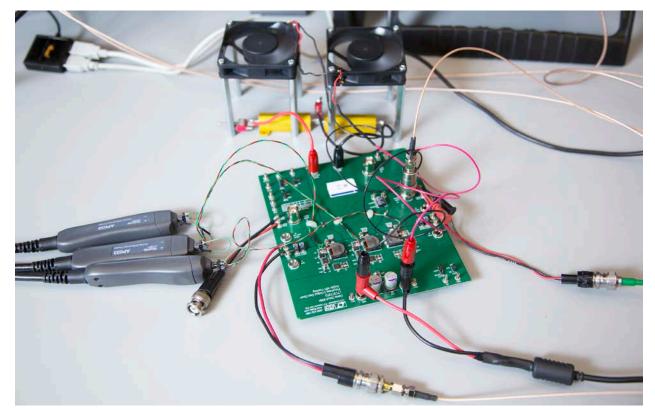

#### **Device Under Test Setup**

DUT: 3-phase non-isolated buck converter

Board courtesy of:

#### Lab Setup

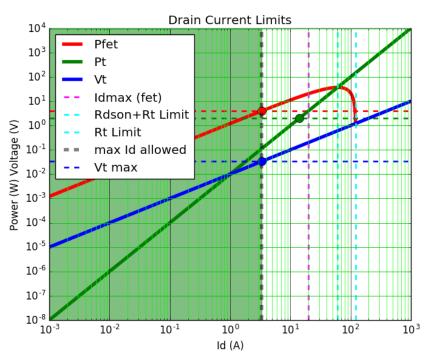

#### **Transient Generator Limits**

- FET max power dissipation: 4 W

- Maximum drain current: 20 A

- Max Vout: 1.22 V

- Source resistor: 10 mOhms, 2W max

- Rdson 10 mOhms

Drain current must be restricted to 3.372 A due to FET power dissipation specification.

At this current, the maximum source resistor voltage (Vt) measured will be 33.72 mV.

Complete list of remaining drain current limitations: 14.14 A allowed due to source resistor power rating. 20.0 A allowed due to fet max drain current specification. 61.0 A possible due to Rdson and source resistor values. anything below this line is not possible based on the values provided.

122.0 A possible due to source resistor value.

UBM

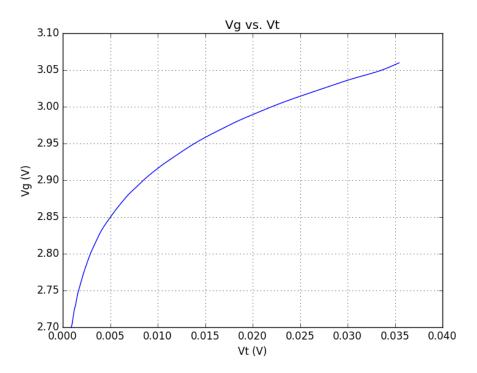

#### **Transient Generator Calibration**

- The FET gate voltage is slowly raised, while measuring the voltage across the source resistor.

- We stop when the voltage across the source resistor reaches the max voltage of 33.72 mV

- A spline is fit to the data so that we can interpolate values of gate voltage needed to generate desired drain currents.

- Idea is to operate in a linear region with given signal swing – bias for class A operation is subtracted from DC load current supplied by electronic load.

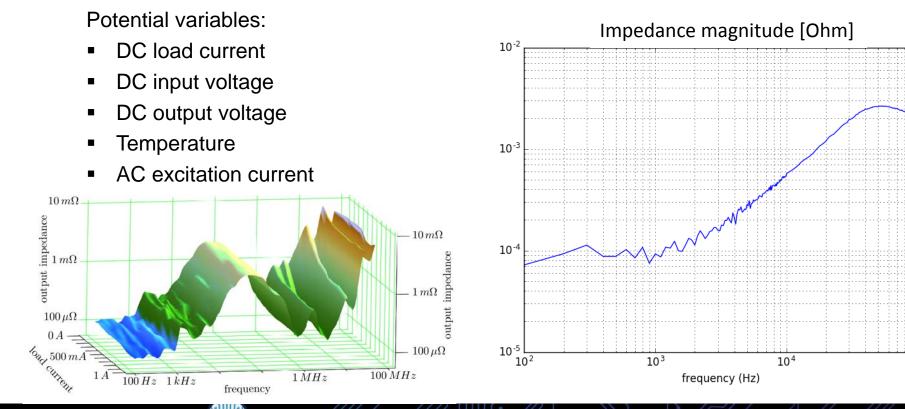

# **Output Impedance vs. DC Load Current (Light Load)**

$10^{5}$

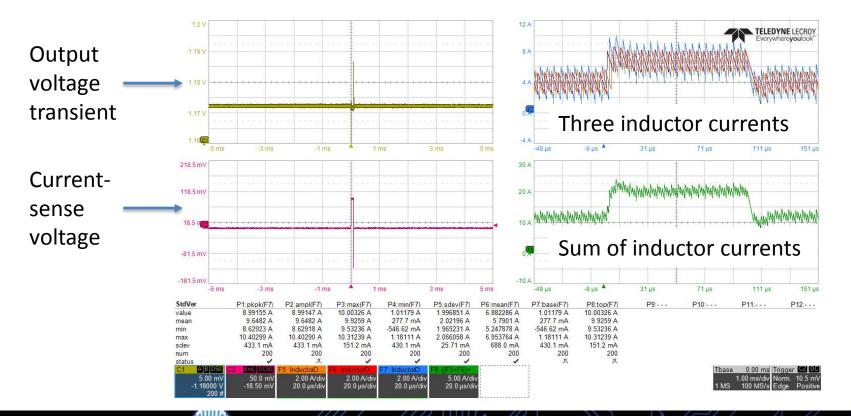

#### **Transient Current Step**

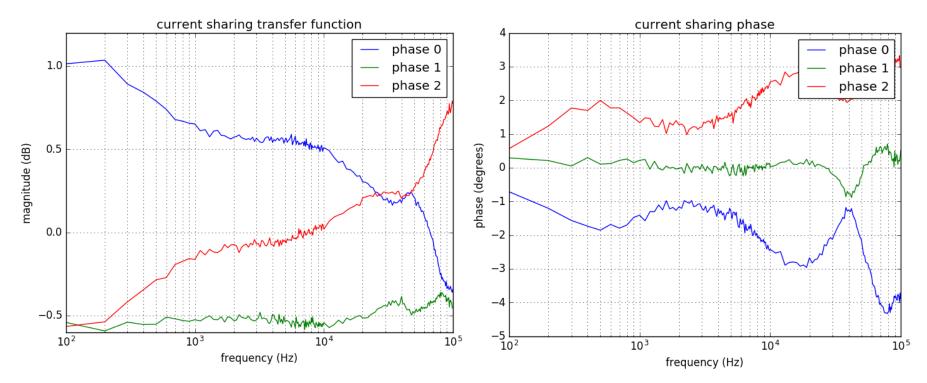

# **Current Sharing vs. Frequency**

# Agenda

- Introduction

- Common PDN Test Tasks

- Universal PDN Test Tool, Concept

- Universal PDN Test Tool, Implementation

- Summary and Conclusions

# Summary

- Various PDN measurement tasks today are covered with different instruments and connections

- A universal PDN test tool is proposed, which produces multiple metrics with the same instruments and minimum number of connections

- Inductor current measurements are possible using Vcs and VL

- Although VL measurement may need low frequency correction

- Next Steps are to use sampled switch node voltage to restore low frequency accuracy

- Extensive calibration is required for any measurement because of large component variability (especially estimation of RL).

- The same instrumentation can be used for time-domain and frequency-domain tests

- Post-processing of inductor currents of multi-phase converters provides current-sharing transfer function

# Thank you!

#### **QUESTIONS?**

JAN 31-FEB 2, 2017