# **DesignCon 2017**

# Why We Love and Hate DC-DC Converters?

**Panel discussion**

## **Panelists:**

Tony O'Brien, Cisco Systems tonobrie@cisco.com

Jordan Keuseman, IBM jkeusema@us.ibm.com

Don J. Nguyen, Intel Corporation don.j.nguyen@intel.com

Istvan Novak, Oracle (\*) istvan.novak@oracle.com

(\*) panel organizer and moderator

#### **Abstract**

DC-DC converters are becoming the staple of electronic designs. They offer high efficiency, small size, light weight, and many advanced functions, such as monitoring various parameters, automated or user-adjustable tuning, etc. The benefits unfortunately come with potential problems: additional switching noise, both low and high frequencies, increased transparency propagating noise between supply rails, more complicated initialization, set up, trouble shooting and debug. This panel discussion brings together some of the OEMs and offer their perspective in terms of available benefits and current challenges and offers an update to the DesignCon 2007 panel discussion "Emerging Challenges of DC-DC Converters".

## **Summary**

DC-DC converters are extensively used in electronic designs. They offer high efficiency, often in the high 80s percentage, sometimes even above 90%. Due to continuously improving component technology, they come in small sizes and light weight. They may also have many advanced functions, such as monitoring temperature, input and output voltages and currents. Some offer automated or user-adjustable tuning of their control loop. The per-phase switching frequency also continues to rise and today converters can easily run at multi-megahertz switching frequencies. The benefits, however, come with potential drawbacks and problems.

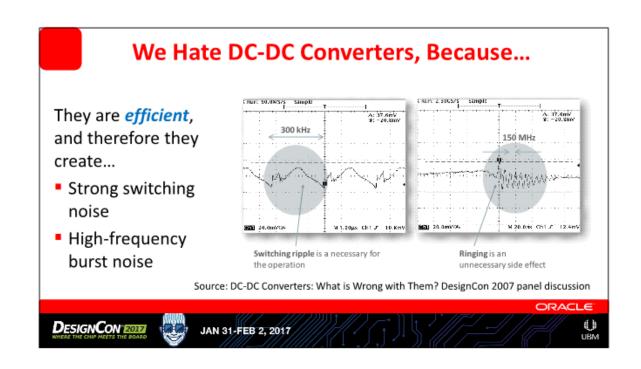

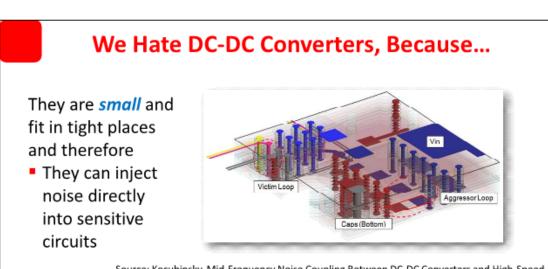

The high efficiency requires a reduction of resistive losses, which can result in increased switching noise, both low and high frequencies. The smaller size is achieved by minimizing input and output filter complexity, which in turn produces increased transparency for noise propagating between supply rails. Some converters today require more complicated initialization, longer set up and more involved trouble shooting and debug. This panel discussion brings together some of the OEMs and offer their perspective in terms of available benefits and current challenges.

This is an update to the DesignCon 2007 panel discussion "Emerging Challenges of DC-DC Converters". In that panel discussion Intel, Hewlett Packard and Sun Microsystems compared notes. Over the past ten years the DC-DC converter density continued to increase, making converters smaller and more efficient, offering more features. This has happened partly due to better components: switching FETs with lower ON resistance and lower dynamic losses, power inductors with lower DC and AC losses, more efficient, denser capacitors. Lower losses, however, increase the tendency of ringing, creating high-frequency interference within the boundaries of our own systems [2], [3]. Ten years later Cisco, IBM, Intel and Oracle review what has happened over the past years: which challenges have remained, which challenges have been solved, which new benefits and challenges emerged.

## **Panelists' Biographies**

**Tony O'Brien** has been designing, specifying, and qualifying power supplies and regulators at Cisco for the past 11 years. Systems range from small 10 W switches and routers to multi-kW core routers. Reliability is paramount and ever increasing platform performance requires smaller, faster, more efficient power systems. Prior to joining Cisco, Tony progressed to senior staff engineer at Artesyn and V.P. of Engineering at Martek Power, developing DC-DC converters and AC-DC power supplies for over 25 years. He has authored papers at APEC, IEEE PELS, and other conferences, and holds two patents in power conversion.

**Jordan Keuseman** joined IBM in 2006. He currently works as a power systems engineer for IBM mid-range and low-end servers responsible for power architecture, design, testing and release. Prior to this role he served as a PCB design engineer also at IBM. He has worked on a number of platforms focusing on POWER based server designs. He has received 9 patents.

**Don J. Nguyen** is a Principle Engineer at Intel Corporation. He joined Intel in 1996 as a Power Technologist. He is responsible for developing power subsystems for phone, tablet, laptop and server applications. Prior to Intel, he worked on battery-operated power systems for small-form factor computing devices, active-matrix display with high-lamination system for avionic displays. His favorite project/components to work on: super-capacitor. His favorite (personal) activity: Fishing.

**Istvan Novak** is a Senior Principle Engineer at Oracle. Besides signal integrity design of high-speed serial and parallel buses, he has been engaged in the design and characterization of power-distribution networks and packages for mid-range servers. He creates simulation models, and develops measurement techniques for power distribution. Istvan has twenty plus years of experience with high-speed digital, RF, and analog circuit and system design. He is a Fellow of IEEE for his contributions to signal-integrity and RF measurement and simulation methodologies.

## **SPEAKERS**

Tony O'Brien

Tech. Lead, Power Systems, Cisco tonobrie@cisco.com | cisco.com

Tony O'Brien has been designing, specifying, and qualifying power supplies and regulators at Cisco for the past 11 years. Systems range from small 10 W switches and routers to multi-kW core routers. Reliability is paramount and ever increasing platform performance requires smaller, faster, more efficient power systems. Prior to joining Cisco, Tony progressed to senior staff engineer at Artesyn and V.P. of Engineering at Martek Power, developing DC-DC converters and AC-DC power supplies for over 25 years. He has authored papers at APEC, IEEE PELS, and other conferences, and holds two patents in power conversion.

JAN 31-FEB 2, 2017

**(,)** ⊔BM

## **DC-DC Converters**

#### o Let's define the topic:

Power Range: 1 W to 1 kW

Input Voltage: 1.8 V to 100 V

Output Voltage: 0.6 V to 60 V

Non-Isolated and Isolated

o Construction: Module, On-Board, or Integrated

#### o What's to Love or Hate?

- . Constant balancing act of:

- o Cost, Efficiency, EMI, Reliability, Size, Stability, etc.

- . Multi-disciplinary skills required:

- o Design: Analog and now Digital control, Magnetics, Thermal, PCB Layout

- . Understanding of materials, component parasitics, and Reliability

JAN 31-FEB 2, 2017

## **Progress since 2007 – and Challenges**

- Efficiency

- Regulated IBC up to 97% up from 85% in 2007

- PoL (Board mount) 90% for 12 V to 1 V up from 80%

- Switching Frequency

- Typ. 300 to 600 kHz up from 100 to 400 kHz

- Power Density

- ¼ Brick module: > 1,000 W up from 250 W

- Power Block module: 50 to 260 A / in<sup>2</sup> New

- On-board PoL: 10 to 40 A / in² up from 2 to 10 A / in²

- . Challenges:

- Thermal management

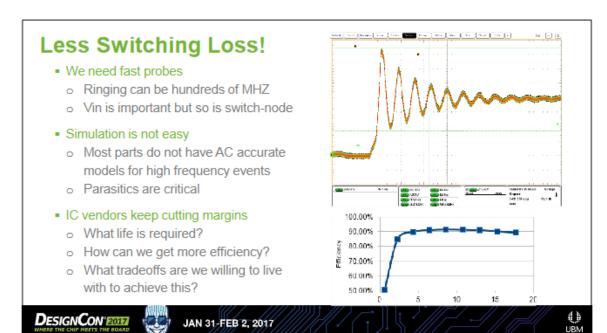

- Fast switching (Voltage spikes, EMI, AC losses, etc.)

- Transient response / Stability

## The Future (more to Love & Hate):

#### o New component technologies

- 。 GaN or GaAs: Frequencies to 5 MHz / smaller size / faster response

- Lower inductance packaging

- Integrated Drivers

- o Capacitor & Magnetics advances to support higher frequencies

#### New topologies

- o Direct 48 V to 1 V conversion

- High Voltage (400 V) bus distribution

- Integrated Voltage Regulators: co-packaged ASIC power (MHz switching)

- Higher power switched capacitor converters

#### o Challenges:

- New aspects to the familiar issues

- o Digital control and communications: is it well behaved over all conditions?

- Component reliability

JAN 31-FEB 2, 2017

## Thank you!

---

**QUESTIONS?**

JAN 31-FEB 2, 2017

()

## PMBus is Great!

- A standard that requires nothing to be implemented

- 1 register being implemented is okay

- Some registers should always be grouped but this isn't the case

- Cost can be prohibitive

- o How much are you willing to pay?

- · Growing pains of early adoption

- AVSBus inconsistencies

- Makes system firmware more reusable

- o But upfront effort is higher

- Nothing is required means there is still vendor specific workarounds in code

- Often requires a dual address (I<sup>2</sup>C and PMBus)

- Still require I<sup>2</sup>C for many features that standard does not easily allow for

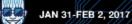

## **All Digital Loops!**

- Except for the non-linear parts

- Many digital loops are too slow for very fast transient response

- Analog loops are not gone

- Simulations just got harder

- Don't worry, it's stable mentality.

- Lab surprises due to poor prediction of behavior

- Fiddle with knobs to fix all things

- Now we get to be firmware engineers too

- Manufacturing code

- Revision control

- Real programming sometimes

- Field patches

- o Ship it, we can always fix it with firmware

JAN 31-FEB 2, 2017

## Reliability Improvements!

- Life testing is virtually nonexistent at IC vendors

- · Cost and schedule prohibit long life testing

- o Many problems are found in the field

- · Push for efficiency above all else

- Commoditization of market leads to heavy pressure to differentiate

- The burden is on the system platform users

JAN 31-FEB 2, 2017

## Wide Band-Gap FETs!

- 5-10 years ago GaN and SiC were supposed to take over for Silicon

- It didn't happen for < 100V applications

- Why has growth slowed?

- Harder to use and unproven

- Silicon improvements greater than expected

- Big gap between theory versus practice for lower voltage uses

- Usage would have opened up new possibilities

- Transformerless topologies for higher Vin

- Higher switching frequencies

Fig. 1. By 2009, the rate of Figure of Merit improvements for silicon-based MOSFETs slowed. In the last few years, GaW-based power FET's began emerging with better FoWs than their silicon-based counterparts.

DESIGNEON 2017

JAN 31-FEB 2, 2017

**(**.) ⊔BM

## **Higher Voltage Power Distribution!**

- 12V to 48V

- I<sup>2</sup>R losses reduced

- More efficient silver-box PSUs

- Easier battery backup topologies

- Telecom market mature

- Still SELV

- Cons

- Requires transformers for high power DC/DC

- o Intermediate or direct conversion

- Added cost

- Power FETs are not tuned for low Vin figure of merit

- Market is not as mature due to lack of good turnkey solutions in this space

- Wide bandgap is not fixing these problems

- Much more complicated tradeoffs for upfront cost versus TCO

## Requirements are Hard!

- di/dt very hard to characterize prior to lab measurements and the converter must design for worst case to hold spec

- Worst-case power spikes can exist only under very specific conditions

- Changes in updateable or pluggable hardware can cause stability problems

DESIGNCON 2017

()

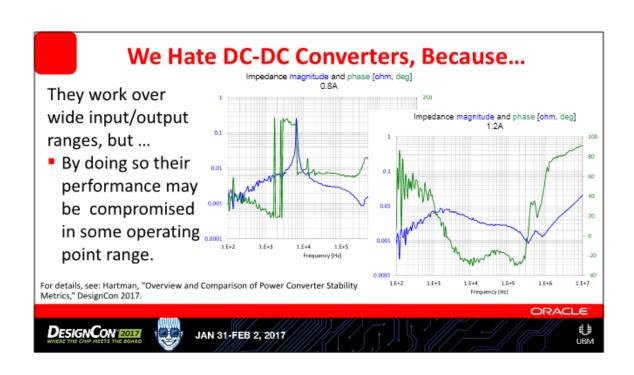

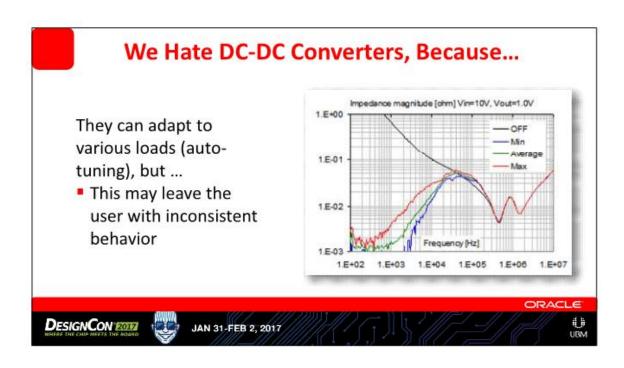

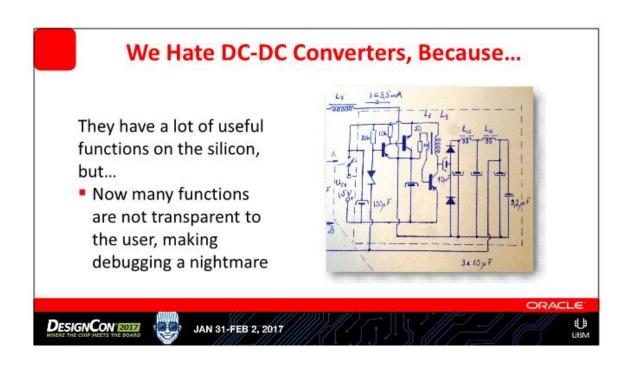

## We Love DC-DC Converters, Because They...

- Are efficient

- Are small

- Work over wide input/output ranges

- Can adapt to various loads

- Have a lot of useful functions on the silicon

Source: Kocubinsky, Mid-Frequency Noise Coupling Between DC-DC Converters and High-Speed Signals. CDNLive, August 31, 2016, Burlington, MA.

**∰** UBM