## Welcome to

# **DESIGNCON® 2020** WHERE THE CHIP MEETS THE BOARD

Expo

Conference

January 28 - 30, 2020

January 29 - 30, 2020

Santa Clara Convention Center

#DesignCon

# **Current Distribution, Resistance, and Inductance in Power Connectors**

Track 10. Power Integrity in Power Distribution Networks

Adam Gregory, Samtec Clement Luk, Samtec Gary Biddle, Samtec Istvan Novak, Samtec Gustavo Blando, Samtec

January 28–30, 2020

#DesignCon

#### **Author Bio**

Adam Gregory is a Signal Integrity Engineer at Samtec. He is involved in modeling and analysis of high-speed differential signaling channels. He received a BSEE and MSEE at the University of South Carolina.

Clement Luk is a Signal Integrity Engineer in Samtec. He is involved in high-speed connector, PCIe application and channel simulation and measurement. He received his BSCS and MSEE from University of Wisconsin-Madison.

Gustavo Blando is a Senior Principle Engineer and leading Principal SI/PI Architect at Samtec Inc. In addition to his leadership roles, he's charged with the development of new SI/PI methodologies, high speed characterization, tools and modeling in general. Gustavo has twenty plus years of experience in Signal Integrity and highspeed circuits.

January 28-30, 2020

#### **Author Bio**

Gary Biddle received his BS in Physics from University of Florida 1976 and MS in Physics from Penn State University 1991. His work experience includes high frequency VNA and EMI measurements, along with nearly 20 years of simulating PCB and interconnect structures. He has published several articles and holds several patents.

Istvan Novak is a Principle Signal and Power Integrity Engineer at Samtec, working on advanced signal and power integrity designs. Prior to 2018 he was a Distinguished Engineer at SUN Microsystems, later Oracle. He worked on new technology development, advanced power distribution and signal integrity design and validation methodologies for SUN's successful workgroup server families. He introduced the industry's first 25um power-ground laminates for large rigid computer boards and worked with component vendors to create a series of low-inductance and controlled-ESR bypass capacitors. He also served as SUN's representative on the Copper Cable and Connector Workgroup of InfiniBand, and was engaged in the methodologies, designs and characterization of power-distribution networks from silicon to DC-DC converters. He is a Life Fellow of the IEEE with twenty-five patents to his name, author of two books on power integrity, teaches signal and power integrity courses, and maintains a popular SI/PI website.

January 28-30, 2020

#### **Outline**

#### Introduction & Background

- Establishing Baseline

- Component Level: DC to High Frequency Simulation to Measurement Correlation

- System Level: SI and PI Interaction

- Conclusions

#### **Introduction & Background**

- This presentation analyzes the frequency dependent resistance and inductance of power connector pin patterns and connection geometries

- Goal is to establish:

- 1) 3D simulator tools are capable of accurately profiling resistance and inductance at the low frequencies relevant for power integrity simulations

- 2) The loss of existing 3D models of connectors correlates with measurement at low frequency

- If these goals are met, there is high confidence that simulation can predict impact to power integrity based on connection schemes in a full system

6

#### **Outline**

#### Introduction & Background

- Establishing Baseline

- Component Level: DC to High Frequency Simulation to Measurement Correlation

- System Level: SI and PI Interaction

- Conclusions

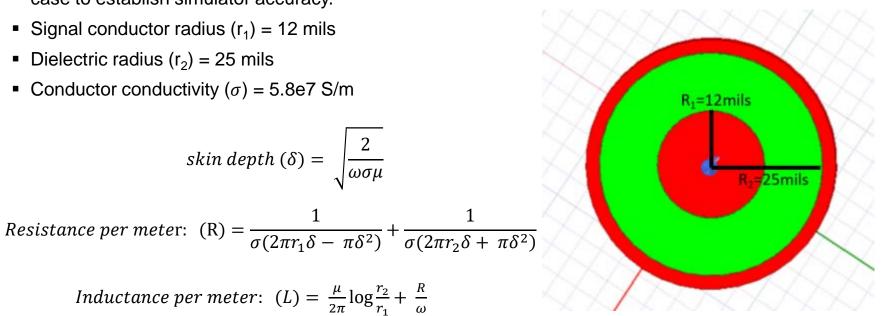

#### **Establish Baseline with Coaxial Cable**

- Coaxial cables have analytical equations for frequency dependent resistance and inductance, so it is a good test case to establish simulator accuracy.

- Signal conductor radius (r<sub>1</sub>) = 12 mils

- Dielectric radius (r<sub>2</sub>) = 25 mils

- Conductor conductivity ( $\sigma$ ) = 5.8e7 S/m

#### Coax Cable cross section

Inductance per meter: (L) =  $\frac{\mu}{2\pi} \log \frac{r_2}{r_1} + \frac{R}{\omega}$

skin depth ( $\delta$ ) =  $\sqrt{\frac{2}{\omega\sigma\mu}}$

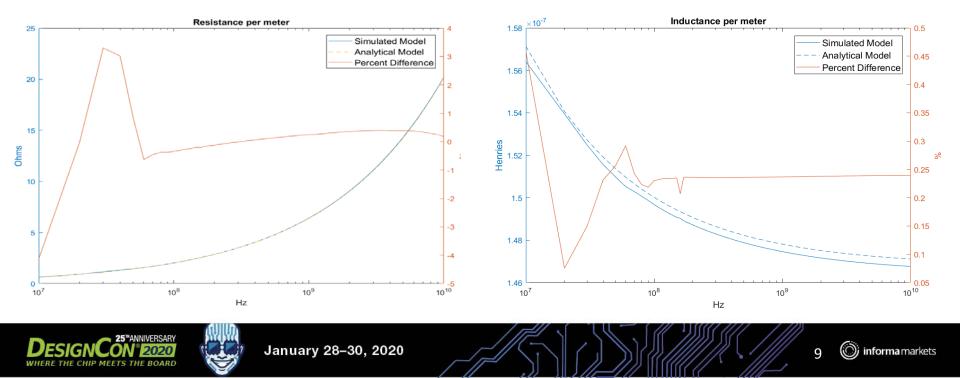

#### **Coaxial Cable Resistance/Inductance**

Simulated results for Resistance and Inductance show a good match to analytical equations. Inductance begins to diverge at low frequencies, but this is more likely shortcomings in the analytical equation.

#### **Convert S-parameter to Resistance & Inductance**

- For medium and high impedances, short one side of 2-port S-parameter to Ground to create 1-port S-parameter

- For small impedances, shorted loops, use Two-port sunt-through scheme

January 28-30, 2020

Solve input impedance (Z<sub>i</sub>), Resistance, and Inductance using equations shown below

One-port reflection:

Two-port transmission:

$$Z_i = Z_0 \frac{1 + S_{11}}{1 - S_{11}} \qquad \qquad Z_i = \frac{Z_0}{2} \frac{S_{21}}{1 - S_{21}}$$

$Resistance = real(Z_i)$

$Inductance = \frac{imag(Z_i)}{\omega}$

### **Approximate Connector w/ Layered Metal**

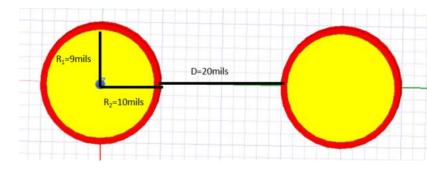

- Simple connector approximation: 2 cylindrical pins in a homogeneous dielectric material.

- Goal is to compare resistance/inductance results for single conductive material vs. a layered metal

- Radius of each pin = 10 mils.

- Center-to-Center pitch = 40 mils

- Single material:

- o Conductivity = 5.8e7 S/m

- Layered material

- o 9 mil radius core with Conductivity = 2.5e7 S/m

- o 1 mil outer layer with Conductivity = 5.8e7 S/m

Cylindrical connector pins with layered metal

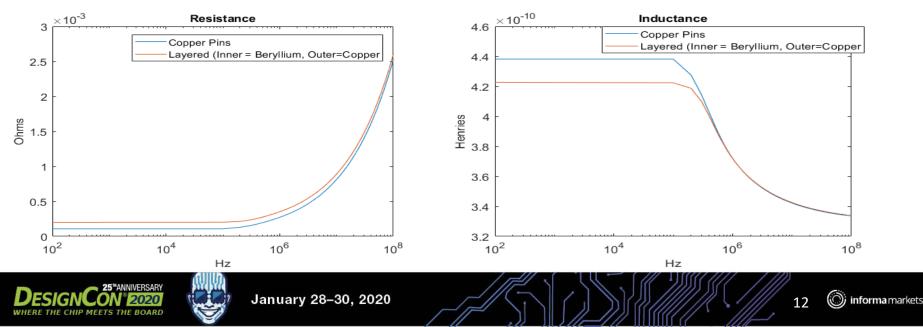

#### Layered metal Resistance/Inductance

- Resistance shows the expected DC offset, and the resistance effectively converges around 100MHz.

- Inductance effectively converges around 1MHz. The skin depth becomes equivalent to 1mil copper around 5MHz. Below 200KHz, there is a 5% decrease in Inductance for the layered pins.

- For this simulation, the layered material accounted for 10% of the total cylinder radius. Actual

products have a much smaller plating depth, so the effect of plating was ignored in the remainder of

studies. The existing connector models use the material of the inner conductor.

#### **Outline**

- Introduction & BackgroundEstablishing Baseline

- Component Level: DC to High Frequency Simulation to Measurement Correlation

- System Level: SI and PI Interaction

- Conclusions

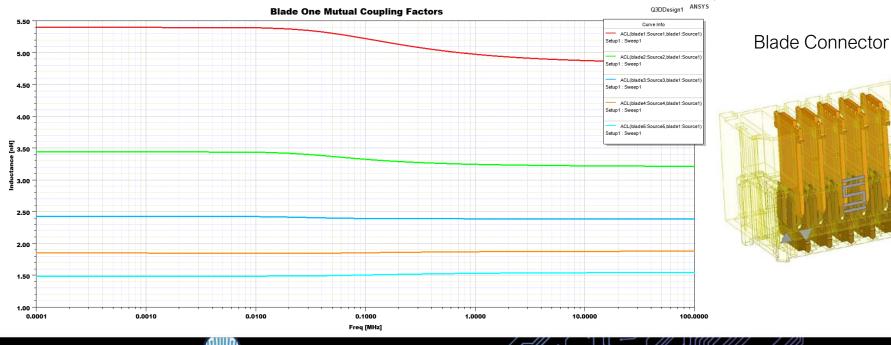

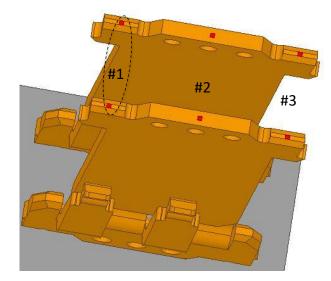

#### **Power Connector Example**

Blade 1 Self Inductance & Mutual Inductances from Blade 1 to all other blades

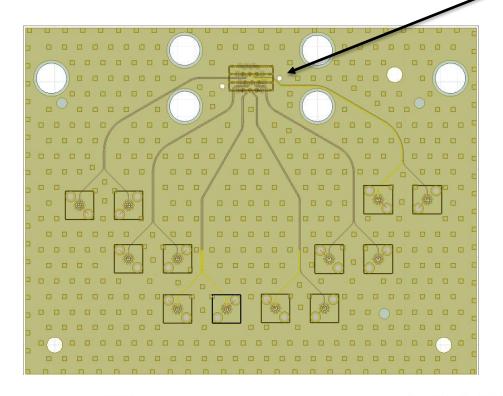

## Simulation Model Design

- Replicates Physical Test Sample [2 blade loop]

- CAD imports to HFSS & Q3D tools

- Multiple Excitation Points to check resolution

- Minimized port excitation effects between tools

#### 2 Blades form Series Impedance Loop

Red Dots represent 3 measurement locations Gray plane represents shorting solder attached to bottom of blades

15

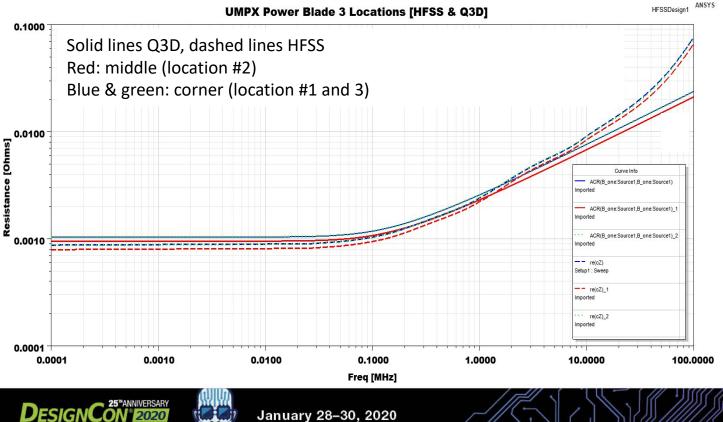

#### **Power Connector: Simulation Resistance Results**

- Location #1 and #3 are symmetric, thus results should be identical

- Both tools show delta for Location #2

16

(i) informa markets

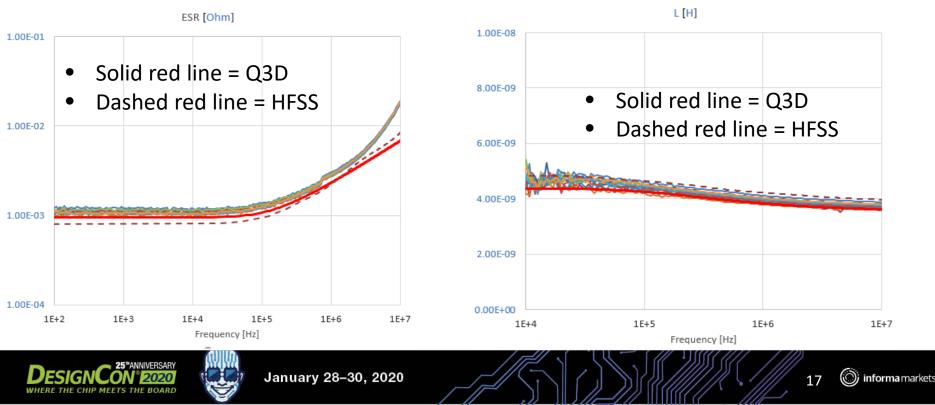

#### **Power Connector: Simulation to Measurement Correlation**

Q3D, HFSS resistance and inductance plots compared to measurements

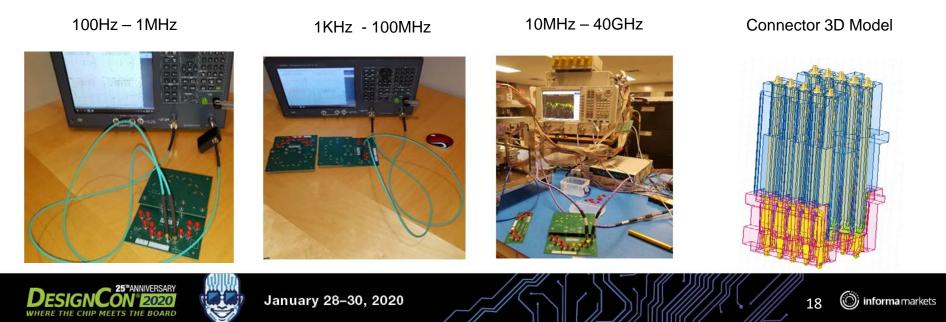

#### **Evaluation Board Measurement setup**

- In addition to the connector which is measured, the board contains SMA connectors, vias, and transmission lines which will be de-embedded for correlation

- Unlike high-speed interconnects, power structures must be measured down to DC. In order to extend the frequency range to high frequencies, 2 VNAs in 3 different setups were used for the frequency ranges noted below

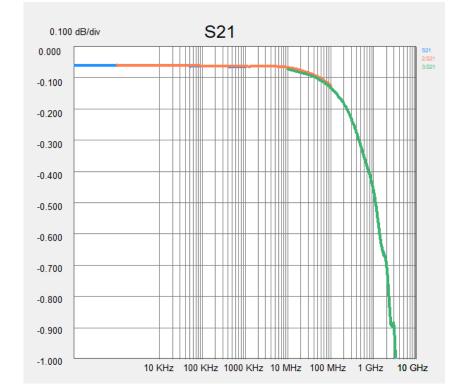

#### **Evaluation Board Measurement Results**

- The plot shows the through measurement of the evaluation board

- The different colored line represent the results from the 3 different VNAs.

- Prior to de-embedding, the 3 VNA results were stitched together into a single curve. The data in the overlap region was weighted to create a single smooth curve across the entire frequency range.

- Separate calibration traces were also measured (and stitched together), and they were used to de-embed the connector itself.

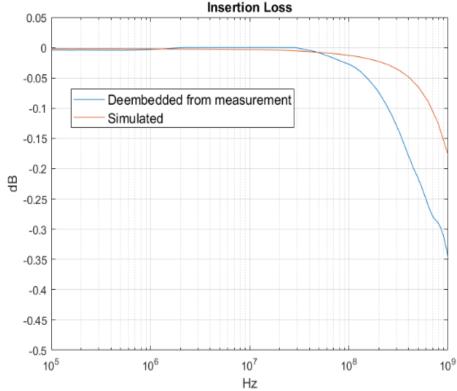

## Simulation to Measurement Correlation: Insertion Loss

- Insertion loss correlates well up to 100MHz.

- Beyond 100MHz, the de-embedded data is more lossy but follows a similar trend vs. simulation

January 28–30, 2020

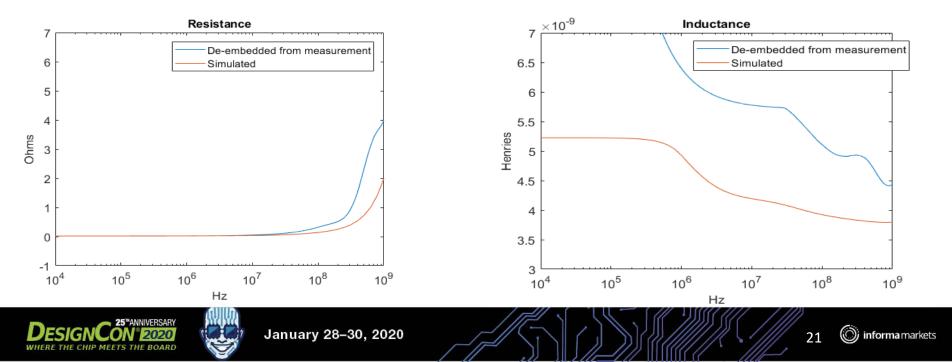

#### Simulation to Measurement Correlation: R(f), L(f)

- The resistance correlation mirrors the insertion loss correlation shown on the previous slide. Good correlation up to 100MHz, but then the de-embedded data shows more resistance

- The de-embedded inductance is problematic below 1MHz (the region where simulations shows roughly constant inductance.) Beyond 1MHz, it shows a similar trend vs. simulation but with 0.5-1nH offset.

#### **Outline**

- Introduction & Background

- Establishing Baseline

- Component Level: DC to High Frequency Simulation to Measurement Correlation

- System Level: SI and PI Interaction

- Conclusions

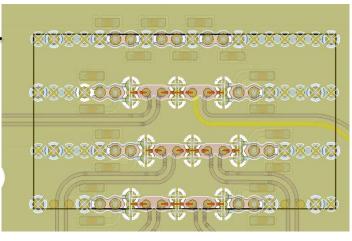

#### **Example: Open Pin Field Connector for Pow & Sig**

Which is better?

|         |   | Т |   |

|---------|---|---|---|

| 1       |   | Т | Т |

|         | Т | Т | Т |

|         | Т | G | Т |

|         | G | G | G |

| Develor | S | G | Р |

| Pow-gn  | S | G | Р |

|         | G | G | G |

|         | S | G | Р |

|         | S | G | Р |

|         | G | Т | G |

|         | Т | Т | Т |

|         | Т |   | Т |

|         |   |   |   |

|         |   |   |   |

|   | Т |   |  |

|---|---|---|--|

| Т | Т |   |  |

| Т | Т | Т |  |

| Т | G | Т |  |

| G | S | G |  |

| S | S | S |  |

| G | G | G |  |

| G | Р | G |  |

| Р | Р | G |  |

| Р | G | G |  |

| G | Т | G |  |

| Т | Т | Т |  |

| Т |   | Т |  |

|   |   |   |  |

nd-sig

Power bundle

3

|   | Т |   |

|---|---|---|

| Т | Т |   |

| Т | Т | Т |

| Т | G | Т |

| G | Р | G |

| G | Р | S |

| G | G | S |

| G | Р | G |

| G | Р | S |

| G | G | S |

| G | Т | G |

| Т | Т | Т |

| Т |   | Т |

Gnd-pow-sig

2

|   | Т |   |

|---|---|---|

| Т | Т |   |

| Т | Т | Т |

| Т | G | т |

| G | G | G |

| G | Р | S |

| Р | G | S |

| G | Р | G |

| G | G | S |

| Р | G | S |

| G | Т | G |

| Т | Т | Т |

| Т |   | Т |

inter-leaving

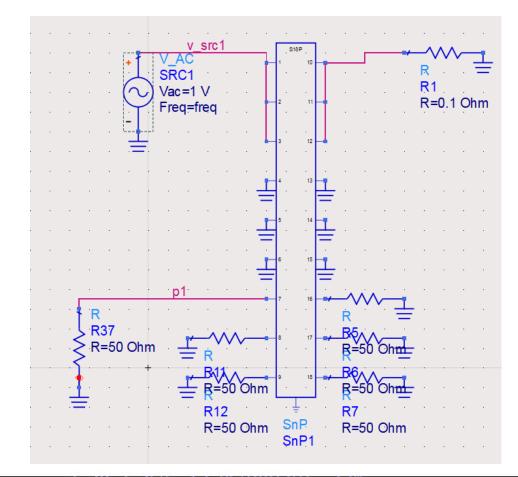

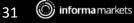

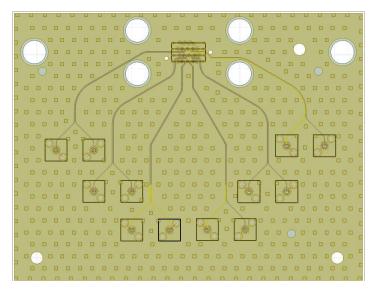

#### **Test Vehicle Setup**

- 6 layers board .

- Blind via.

- DUT: open pin filed mezzanine connector.

- Same board as de-embedded connector measurement from earlier

## Methodology

- 1V at the power pins.

- 0.1Ω as loading.

- User assigned ground are grounded.

- Signal pins are terminated by 50Ω.

- We use ADS for verification only.

- Actual simulation is done in Matlab by solving the modified nodal analysis (MNA) matrix.

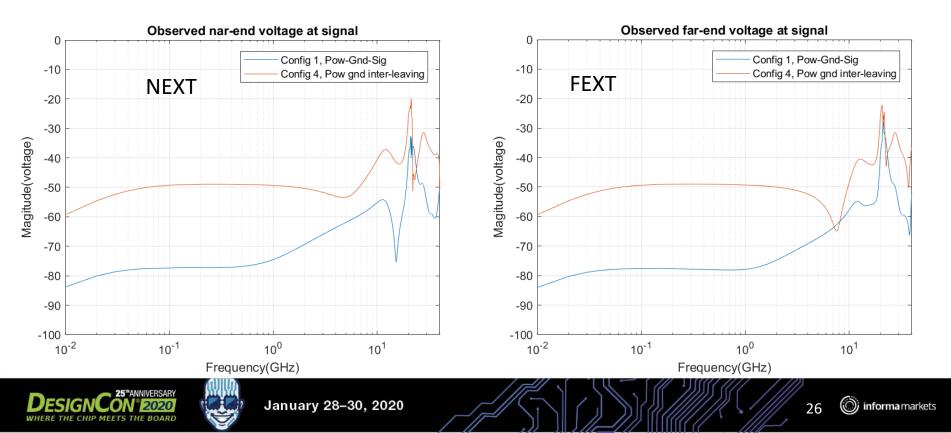

#### **Connector Only Crosstalk is Minimal**

• Take config 1 (pow-gnd-sig) and config 4 (pow gnd inter-leaving) as an example.

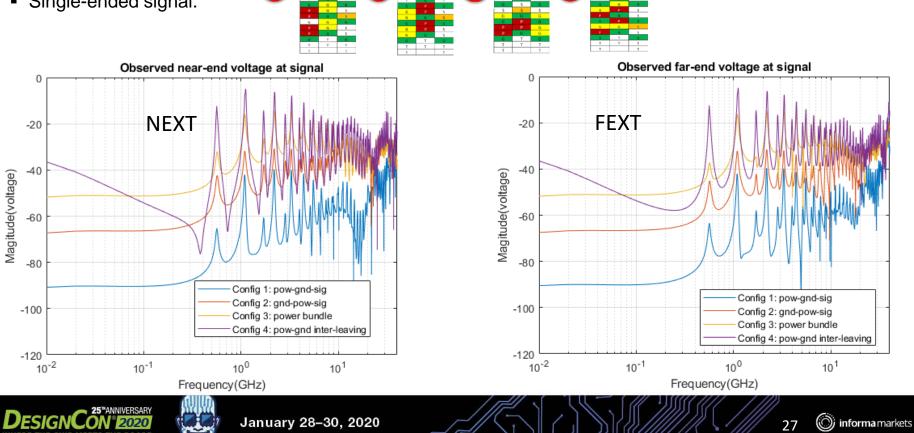

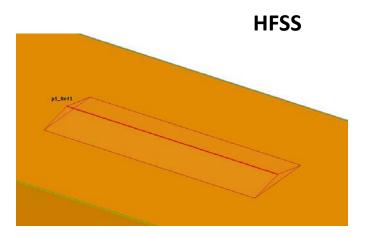

#### Board + Connector + Board, Config 1 to 4

2

Single-ended signal.

3

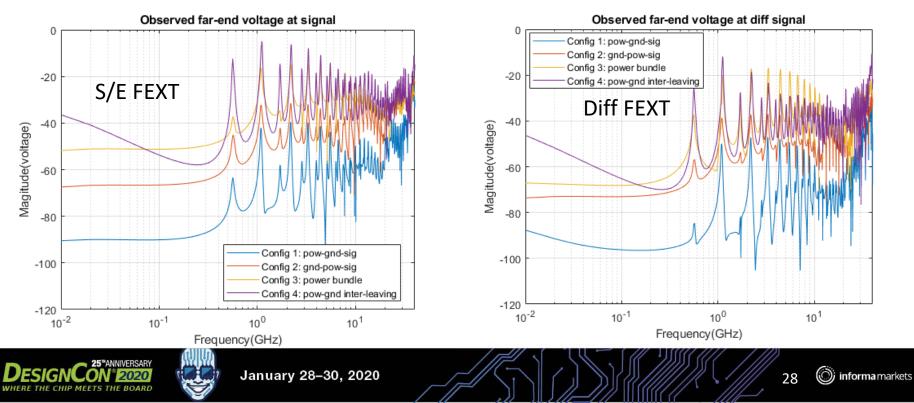

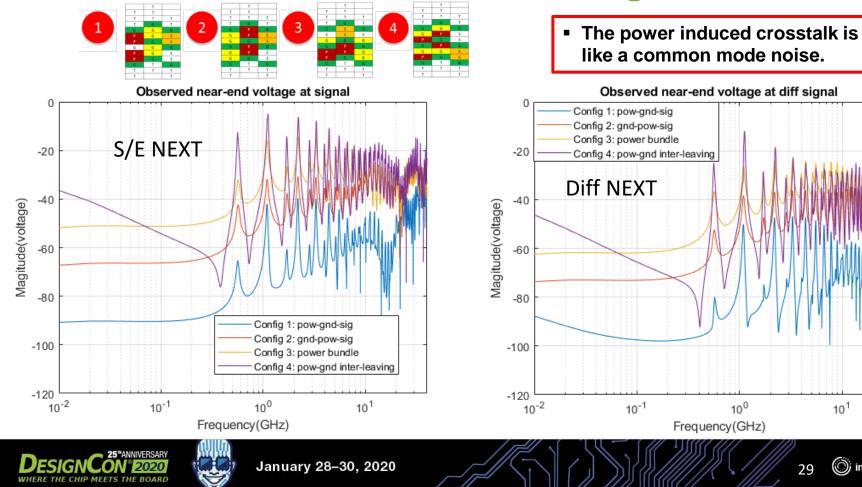

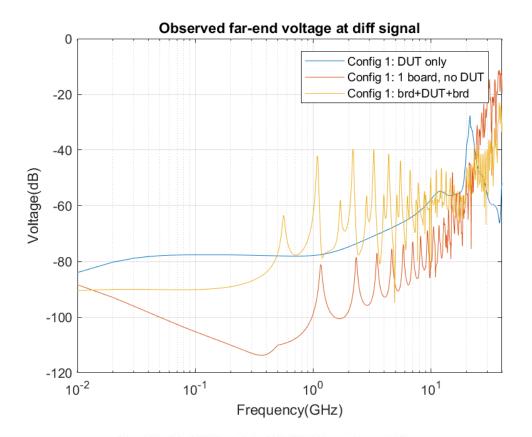

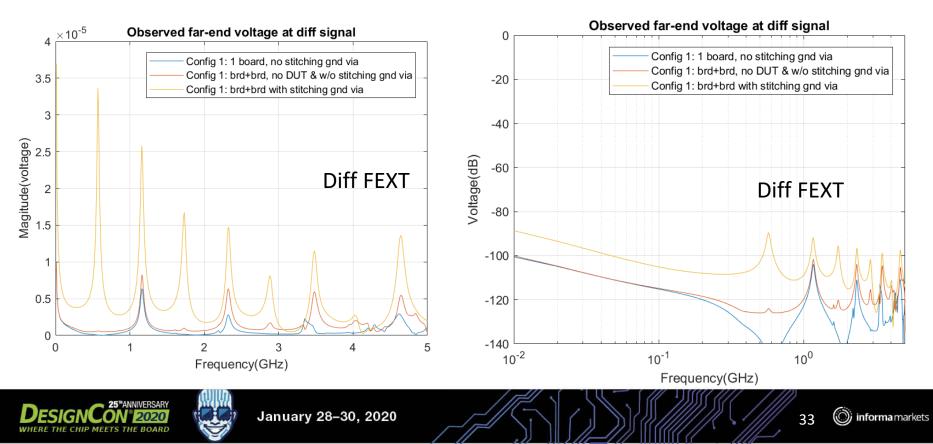

#### **Do Differential Signals Minimize the Crosstalk?**

The power induced crosstalk is like a common mode noise.

#### Board + Connector + Board, Config 1 to 4

() informamarkets

10<sup>1</sup>

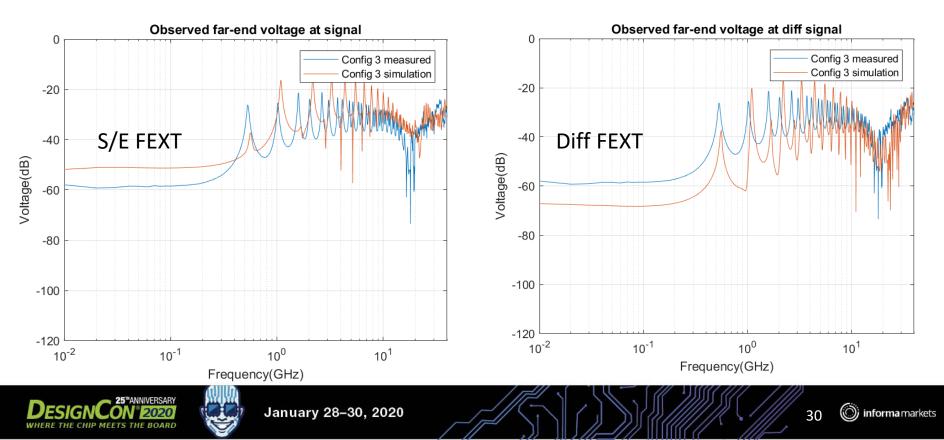

#### **Simulation & Measurement Correlation**

Measured magnitude is more subdued.

## **Spikes in FEXT?**

- From the board!

- With just one board, we also observe spikes in FEXT.

- With the connector, it simply shifts the curve up.

#### What If Stitching Vias Are Removed?

#### With ground stitching via

Ground stitching vias removed except at the edge

January 28–30, 2020

#### **Not From The Plane Resonance...**

• With or without stitching vias, it still pick up the spikes.

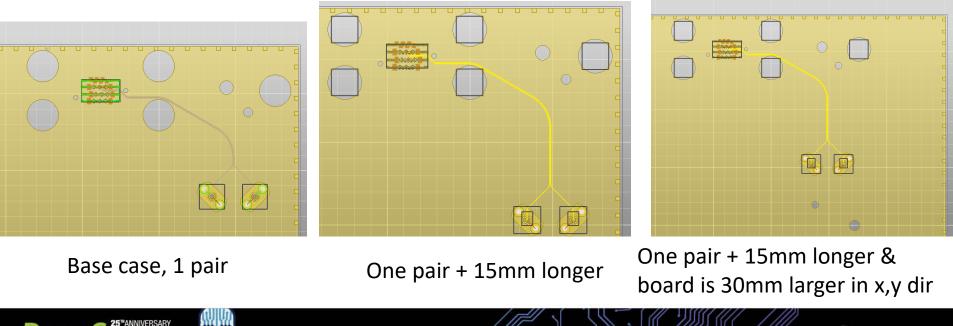

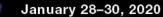

#### **Further Investigation With Just One Pair**

#### **One Pair Investigation Result**

- Not from the plane.

- Longer trace shifts to lower frequency but there is still spike to begin with?

#### What About Via Discontinuities?

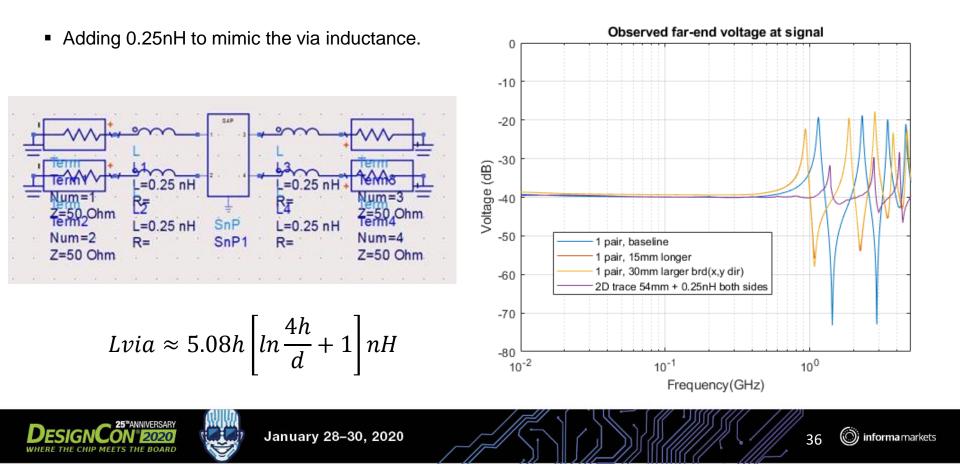

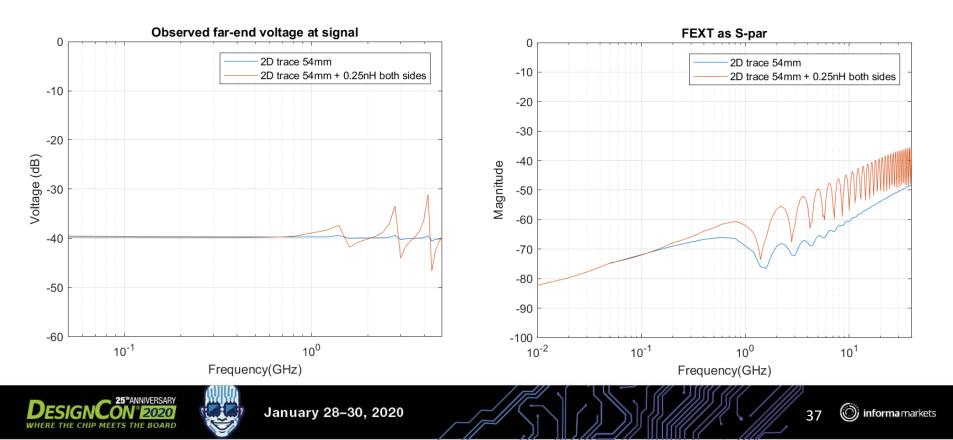

#### **2D Trace vs. 2D Trace + Inductance**

Adding the inductance (discontinuity) creates the spikes!

#### **Outline**

- Introduction & Background

- Establishing Baseline

- Component Level: DC to High Frequency Simulation to Measurement Correlation

- System Level: SI and PI Interaction

- Conclusions

#### **Conclusions**

- Simulation tools seem capable of predicting low high frequency resistance and inductance profiles.

- Isolated connector measurements correlate well vs. simulation.

- De-embedded connector measurements show fair correlation. Resistance is good, but deembedded inductance was problematic at low frequency for SI test board.

- Power induced crosstalk is both board and pinout dependent.

o Interleaved power/gnd pin assignments are not optimal for signal to power crosstalk

o In this particular test board setup, power-gnd-signal pinout gives the minimal induced crosstalk.

- Crosstalk in the connector is accentuated by the board crosstalk.

- Minimizing reflection discontinuities is essential for resonance free crosstalk.

#### Acknowledgement

The authors wish to thank

- Scott McMorrow of Samtec

- Jim DeLap of Ansys

- David Michaud of Samtec

- Jean-Remy Bonnefoy of Samtec

for their valuable comments, help and support.

## Thank you!

#### **QUESTIONS?**

January 28–30, 2020

informamarkets

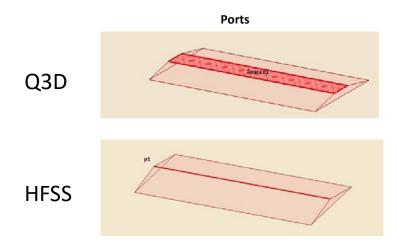

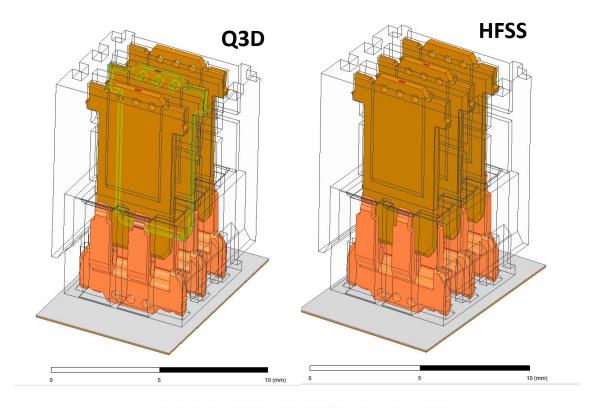

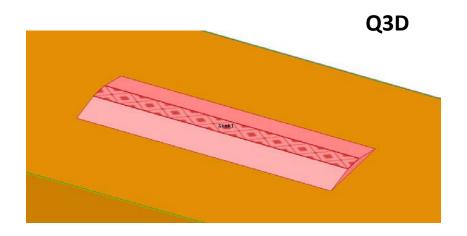

### **Identical CAD for Simulation Correlation**

- Same exact geometry

- Same material properties

- Only difference is slightly different terminal geometry.

- Q3D ... Source and Sink on faces

- HFSS ... Circuit Ports on edge

#### **Difference in Port Definition Geometry**

• .0025 mm in shift in path length

January 28-30, 2020

#### **Side Notes on the Metric**

1) S-parameter assumed  $50\Omega$  at each port.

2) Another difference is due to post-processed Y matrix:

- a) combines columns (v1=v2=..., pow pins at same V)

- o b) combines rows (I1+I2+.., distributed current)

#### **DC Resistance of Layered Metallic Cylinder**

Convert to equation form:

IA=inner area = 9 mils

IS = inner sigma = 2.5e7

- IR = inner resistance = 1/IA/IS\*Length = 3.0943e-04

- OA = outer area = pi\*R\_outer^2 pi\*R\_inner^2 = 3.8510e-08

OS = outer sigma = 5.8e7

OR = outer resistance = 1/OA/OS\*Length = 5.6860e-04

Total resistance = IR & OR in parallel = 2.0038e-4

basically identical to Q3D output