# Welcome to DESIGNCON® 2021 WHERE THE CHIP MEETS THE BOARD

Conference

August 16 – August 18, 2021

Expo

August 17 – August 18, 2021

San Jose McEnery Convention Center

AUGUST 16-18, 2021

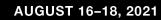

# A Case Study in the Development of 112 Gbps-PAM4 Silicon and Connector Test Platform

Jean-Remy Bonnefoy (Samtec)

Ted Ballou, Istvan Novak, Gustavo Blando, Scott McMorrow (Samtec) Raj Mahadevan (Alphawave IP)

#### **SPEAKER**

#### **Jean-Remy Bonnefoy**

Systems engineer, Samtec jean-remy.bonnefoy@samtec.com

Jean-Remy Bonnefoy is a Systems Engineer for Samtec's Signal Integrity Group. He is involved in the design of high-speed test systems, and he leads the hardware development of evaluation and demonstration platform for high data rate interconnects.

### OUTLINE

- Optimizing a 112G test channel

- Power delivery network

- Channel performance

- Summary and conclusions

### OUTLINE

#### Optimizing a 112G test channel

- Power delivery network

- Channel performance

- Summary and conclusions

## **Optimizing a 112G-PAM4 test channel**

#### Challenges and goals:

- Design an evaluation platform for 112G-PAM4 silicon and connector system

- 3 dB total II at 28 GHz for TX lanes 0

- o Use affordable, readily available material

#DesignCor

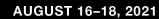

### **PCB design**

#### Stackup:

- o I-Tera MT40

- o 1067 weave

#### Impedance:

- o 90 Ohm package / 50 Ohm single ended coax cables

- ➢ 92 Ohm BGA escape and open routing

- Routing:

- Two routing layers (RX, TX)

- o Short TX traces, 11 mm

- o Board rotation to mitigate periodic fiber weave effects

|            | Calc             |                        |                                      |               |

|------------|------------------|------------------------|--------------------------------------|---------------|

| Layer      | Thickness        | Primary Stack          | Description                          | Dk / Df       |

| Layer - 1  | 0.0010<br>0.0026 |                        | Taiyo 4000-MP<br>1/2oz Mix (Std Plt) | 3.60 / 0.0190 |

|            | 0.0050           | 0.0050 (2-1067)        | I-Tera MT40                          | 3.17 / 0.0023 |

| Layer - 2  | 0.0006           |                        | 1/2oz Sig                            |               |

|            | 0.0052           | 1067 - 76%             | I-Tera MT40                          | 3.08 / 0.0020 |

| Layer - 3  | 0.0006           |                        | 1/2oz P/G                            |               |

|            | 0.0050           | 0.0050 (2-1067)        | I-Tera MT40                          | 3.17 / 0.0023 |

| Layer - 4  | 0.0006           |                        | 1/2oz Sig                            |               |

|            | 0.0052           | 1067 - 76%             | I-Tera MT40                          | 3.08 / 0.0020 |

| Layer - 5  | 0.0006           |                        | 1/2oz P/G                            |               |

|            | 0.0140           | 0.0140 (2-2116/1-3313) | I-Tera MT40                          | 3.56 / 0.0033 |

| Layer - 6  | 0.0006           |                        | 1/2oz P/G                            |               |

|            | 0.0052           | 1067 - 76%             | I-Tera MT40                          | 3.08 / 0.0020 |

| Layer - 7  | 0.0006           |                        | 1/2oz Sig                            |               |

|            | 0.0050           | 0.0050 (2-1067)        | I-Tera MT40                          | 3.17 / 0.0023 |

| Layer - 8  | 0.0006           | 1007                   | 1/2oz P/G                            |               |

|            | 0.0052           | 1067 - 76%             | I-Tera MT40                          | 3.08 / 0.0020 |

| Layer - 9  | 0.0006           |                        | 1/2oz Sig                            |               |

|            | 0.0050           | 0.0050 (2-1067)        | I-Tera MT40                          | 3.17 / 0.0023 |

| Layer - 10 | 0.0026<br>0.0010 |                        | 1/2oz Mix (Std Pit)<br>Taiyo 4000-MP | 3.60 / 0.0190 |

AUGUST 16-18, 2021

### Via breakout optimization

- Topology:

- Top-mounted BGA / Bottom-mounted connector 0

- CDD and through vias, inherent minimal stubs 0

#### Impedance control:

- Auxiliary ground vias

- Teardrops 0

- Offset ground relief on lower reference plane 0

Connector via

CDD via

Thru via

8

AUGUST 16-18, 2021

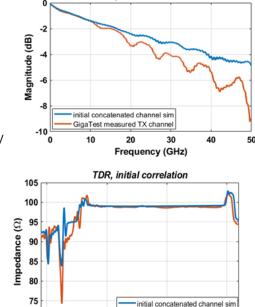

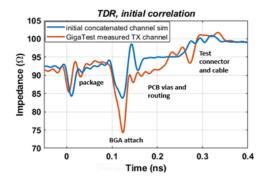

### Initial simulations and measurements

- Concatenated 4-port channel:

- Extracted package layout

- Simulated GL102 dielectrics 0

- Vias, PCB and cabling simulated separately

- Measurements:

- Bare-die BGA package

- Miscorrelation:

- Under-modeled impedance discontinuities

- Missing resonances in the IL 0

0.5

IL. initial correlation

q

AUGUST 16-18, 2021

70

0

#DesignCor

1.5

GigaTest measured TX channe

1

Time (ns)

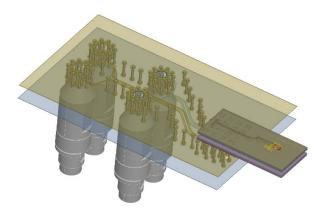

### **Examining root cause**

#### Deep dive simulation review:

- Package vias

- Package copper roughness

- $\circ~$  PCB thru vias

- o Connector model truncated

- Co-meshed simulation

#### Combined co-meshed simulation model

AUGUST 16–18, 2021

////////

#DesignCor

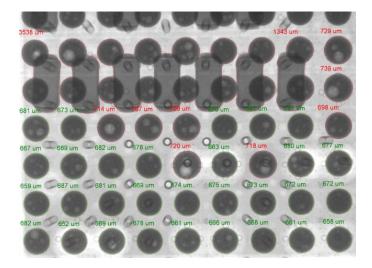

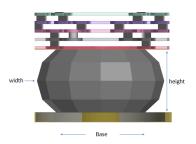

### Key discontinuity = solder attach

- BGA ball size impact on SI

- Reflowed ball shape predicts TDR discontinuities

Real solder ball shapes

Pre-reflow solder ball

CT-scan of soldered BGA

AUGUST 16-18, 2021

#DesignCon

11 🔘

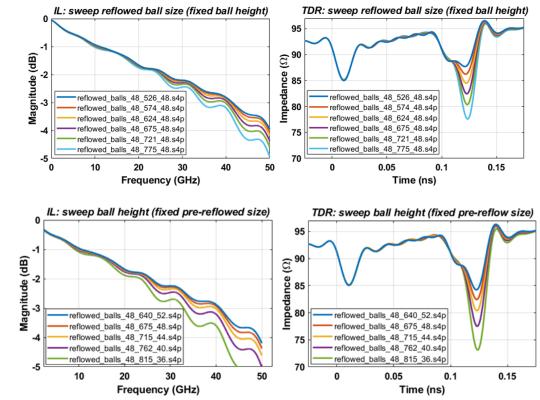

### Solder ball model sweep

Reflowed ball size (width) sweep

Ball shape (height) sweep

#DesignCon

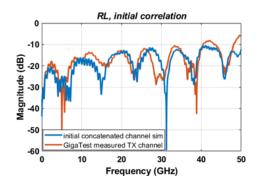

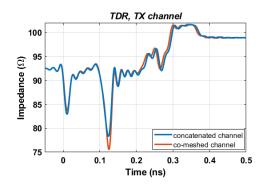

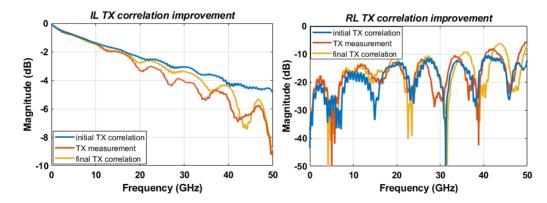

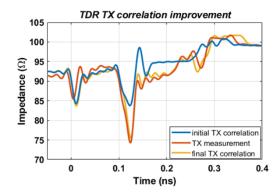

### **Improved correlation**

- Co-meshed simulation:

- Trace impedance updates

- Improved reflowed solder ball model

- Correlation:

- Still missing some IL resonance at higher frequencies

- · Ball model approximation

- Die probe calibration impact

- Small uncertainty in VNA accuracy

#DesignCor

AUGUST 16-18, 2021

13 (informa markets

### OUTLINE

- Optimizing a 112G test channel

- Power delivery network

- Channel performance

- Summary and conclusions

### **Power delivery**

#### Goals:

- $_{\circ}$   $\,$  Power the board from single 5V supply

- Provide option to feed each rail from its own supply

- $_{\circ}$   $\,$  Neglect impact of noise on the board PDN  $\,$

| Net     | DC voltage<br>[V] | Max current<br>[A] | Max<br>transient<br>current [A] | Allowed<br>deviation<br>[mV] | Target<br>impedance<br>[mOhm] |

|---------|-------------------|--------------------|---------------------------------|------------------------------|-------------------------------|

| P_VDD   | 0.75              | 3                  | 1.5                             | 3                            | 2                             |

| PA_VDDL | 0.75              | 2                  | 1                               | 2                            | 2                             |

| PA_VDDH | 1.2               | 2                  | 1                               | 2                            | 2                             |

| P_VDDH  | 1.8               | 1                  | 0.5                             | 1                            | 2                             |

#### Architecture:

Relatively low current = cascaded linear regulators and jumper selectable supply options.

#DesignCon

AUGUST 16-18, 2021

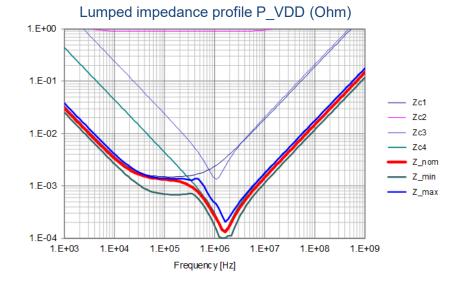

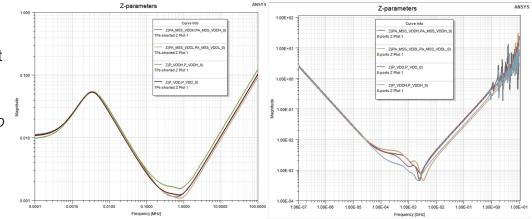

## **Capacitor selection**

#### Big-V impedance profile:

- $_{\circ}$   $\,$  10 uF 0402 ceramic on back of chip  $\,$

- Single value

- Directly on power/gnd pins

- 470 uF polymer bulk capacitors help regulator maintain low impedance

- 22 uF ceramic at the output of the regulators for stability

| Four parallel capacitor banks | C1       | tol. [%] | C2       | tol. [%] | C3       | tol. [%] | C4       | tol. [%] |          |

|-------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Capacitance C [F]:            | 4.70E-04 | 20       | 1.00E-04 | 20       | 2.20E-05 | 20       | 1.00E-05 | 20       | Fmin[Hz] |

|                               |          | -20      |          | -20      |          | -20      |          | -20      | 1.E+03   |

| Ser. resistance ESR [ohms]:   | 0.015    | 0        | 0.9      | 0        | 0.004    | 20       | 0.005    | 20       | Fmax[Hz] |

|                               |          | -50      |          | -50      |          | -20      |          | -20      | 1.E+09   |

| Ser. inductance ESL [H]:      | 3.00E-09 | 20       | 5.00E-09 | 20       | 1.00E-09 | 20       | 1.00E-09 | 20       |          |

|                               |          | -20      |          | -20      |          | -20      |          | -20      | Total:   |

| Number of parts in bank       | 10       |          | 1        |          | 3        |          | 36       |          | 50       |

#DesignCor

AUGUST 16-18, 2021

16 (informa markets

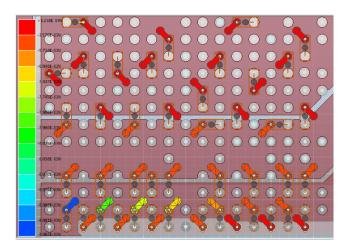

### **PDN** analysis

#### Optimize DC-drop

- $_{\circ}$  1 oz copper power layers

- $_{\circ}$   $\,$  Hybrid solder iteration to optimize shape size

#### Minimize rail-to-rail crosstalk

- Avoid overlap between power planes of different nets.

- Especially analog vs digital nets

| Net     | DC voltage | Max current | Max DC    | Max rel. DC |

|---------|------------|-------------|-----------|-------------|

|         | [V]        | [A]         | drop [mV] | drop [%]    |

| P_VDD   | 0.75       | 3           | 5.1       | 0.68        |

| PA_VDDL | 0.75       | 2           | 4.3       | 0.57        |

| PA_VDDH | 1.2        | 2           | 8.1       | 0.675       |

| P_VDDH  | 1.8        | 1           | 0.53      | 0.03        |

#DesignCon

AUGUST 16–18, 2021

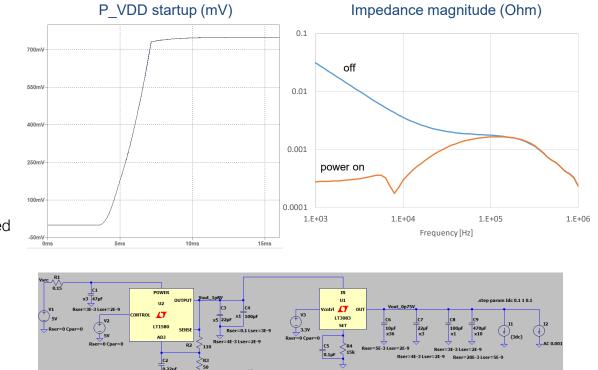

### **PDN** analysis

#### Spice simulations

- $_{\circ}~$  Vendor supplied models and simulator

- Simulated startup behavior to ensure stability of cascaded regulators

- Simulated output impedance with lumped external components

.ac dec 100 100 1E7

AUGUST 16-18, 2021

#DesignCon

18 (informa markets

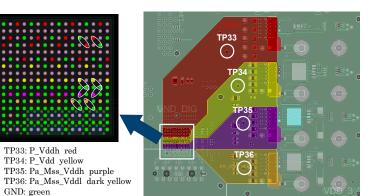

### **PDN** analysis

- AC impedance simulations

- Dedicated test points and chip's pin field location

- Mimicking two-port shunt-through measurement

#### Two scenarios:

- Voltage regulator output open (right)

- Series R-L element mimicking regulator output impedance (left)

- Equivalent inductance intentionally high to see bulk capacitance impedance

AUGUST 16-18, 2021

#DesignCon

19 (informa markets

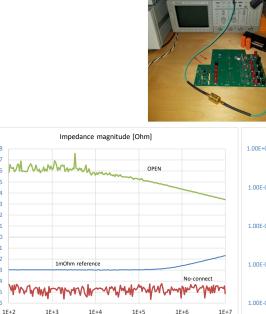

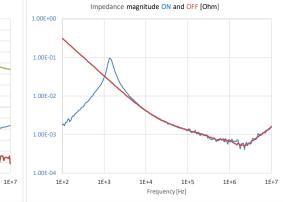

### **Measurements and correlation**

#### Measurements:

- VNA with common-mode toroid suppresses cablebraid ground-loop error

- Home-made semirigid probes

- 100 Hz 10 MHz measurements with and without power applied

#### Miscorrelation:

- DC resistance above 10 mOhm

- Selection jumpers simulated with zero resistance

- Not shown jumpers were shorted with solder

- Impedance peak at 12 kHz around 100 mOhm with minimum load current

Frequency [Hz]

1.00E+08

1.00F+07

1.00E+06

1.00E+04 1.00E+03 1.00E+02

1.00E+01

1.00E+00

1.00E-01 1.00E-02

1.00E-03 1.00E-04

1.00E-05 1.00E-06 - E4 . E4 64

AUGUST 16-18, 2021

#DesignCor

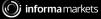

### **Root cause analysis**

- Investigation:

- Disabled upstream regulator

- Added lossy bulk capacitors

- Altered the regulator's feedback circuit

- Measured evaluation board of regulator

#### Improvements:

- Updated regulator model's closed loop bandwidth

- BOM change, higher ESR bulk capacitor

#DesignCor

AUGUST 16-18, 2021

21

(informa markets

### OUTLINE

- Optimizing a 112G test channel

- Power delivery network

- Channel performance

- Summary and Conclusions

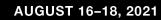

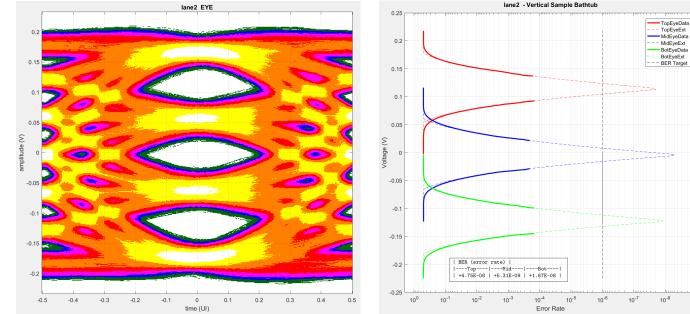

### **Channel performance**

- Clean transmitter PAM4 eye diagram at 106.25Gbps

- Sampling scope with de-embedding tool

#DesignCor

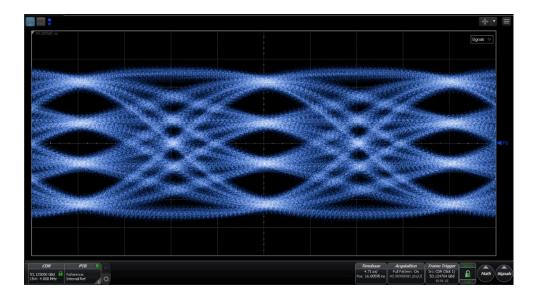

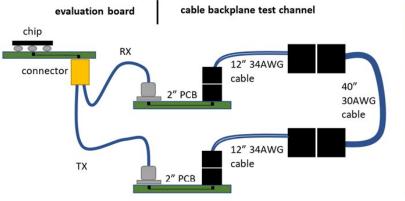

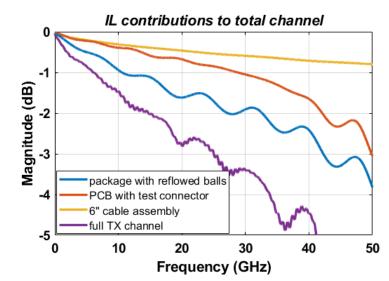

### **Channel performance**

Cable backplane test channel

#### Cascaded channel IL (dB)

#DesignCon

### **Channel performance**

Receiver eye diagram

BER curve

#DesignCon

BER << 1e-4</li>

10-

AUGUST 16-18, 2021

25

informa markets

### OUTLINE

- Optimizing a 112G test channel

- Power delivery network

- Channel performance

- Summary and Conclusions

### **Summary and Conclusions**

#### Successful design enabling 112G-PAM4 silicon evaluation

- $_{\circ}$   $\,$  Low insertion loss TX and RX design

- Clean power distribution

- Good channel performance

#### Important learnings

- o Under-modeled loss contribution of the package

- BGA package attach cannot be neglected for high data rates

- $_{\circ}$   $\,$  Testing power converters prior to design

#DesignCor

AUGUST 16-18, 2021

27 🔘

# Thank you!

#### **QUESTIONS?**

#DesignCon

informa markets